# SC1462 单通道 16 位 ADC

### 主要性能

- 250kHz 采样率

- 输入范围: 4V,5V,10V,±3.3V,±10V,±5V

- ±2 LSB INL<sub>MAX</sub>, ±1 LSB DNL<sub>MAX</sub>

- 16 位无失码

- 具有菊花链 (TAG) 功能的 SPI 串行输出

- 5 V 模拟电源

- 支持 3.3V~5.5V 数字电源

- 使用内部或外部参考

- 250 KSPS 时的典型功耗为 70mW

- 简单的 DSP 接口

- 20 引脚 SOIC 和 28 引脚 TSSOP 封装

### 应用场合

- 工业过程控制

- 数据采集系统

- 数字信号处理

- 医疗器材

- 仪表

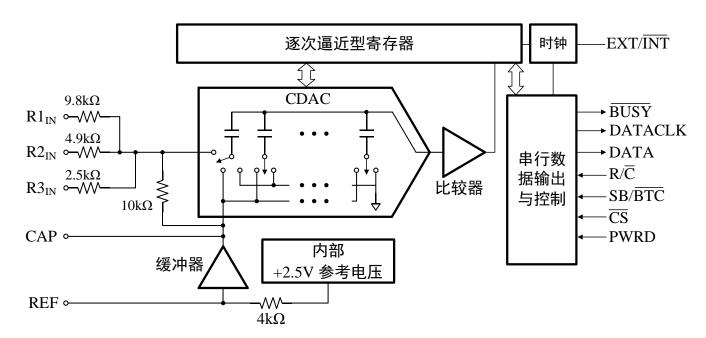

# 功能模块示意图

图 1 功能模块示意图

### 产品概况

SC1462 是一款采用了先进 CMOS 结构的 16 位模数转换器,内部有一个 16 位 SAR A/D 转换器,具备采样保持、参考、时钟以及串行数据接口等功能。数据不仅可以使用内部时钟输出,也可以外部数据时钟同步。在封装设计上,SC1462 可同时支持 20 引脚的 SOIC 封装和 28 引脚的TSSOP 封装,两种封装均支持 SC1462 在-40℃至 85℃的温度范围内正常工作。

SC1462 在整个温度范围内,额定采样率可达 250kHz; 精密电阻器提供了±10V 和 0~5V 等各种输入范围。 SC1462 可以实现在单个+5V 电源工作条件下,功耗低于 100mW,另外数字电源兼容 3.3V~5.5V 供电。

此外, SC1462 还可以输出同步脉冲以便与标准 DSP 处理器配合使用。

# 景目

| 主要性能           |    |

|----------------|----|

| 应用场合           |    |

| 功能模块示意图        | 1  |

| 产品概况           | 2  |

| 目录             | 3  |

| ADC 特性         | 4  |

| 模拟规格与 ADC 特性参数 | 4  |

| 数字规格           | 6  |

| 极限参数           | 7  |

| ESD 保护         | 7  |

| 管脚(焊盘)配置及功能说明  | 8  |

| 时序要求           | 9  |

| 时序参数测量信息       | 10 |

| 使用说明           | 16 |

| 基本操作           | 16 |

| 读取数据           | 16 |

| 内部 DATACLK     | 16 |

| 外部 DATACLK     | 17 |

| TAG 特性         | 18 |

| 模拟输入           | 19 |

| 外形尺寸           | 25 |

| 订购信息           | 25 |

# ADC 特性

# 模拟规格与 ADC 特性参数

表 1 模拟规格与 ADC 特性

| 为                | 数           | 条件         | 最小值  | 典型值  | 最大值      | 单位      |

|------------------|-------------|------------|------|------|----------|---------|

| 分辨率              |             |            |      | 16   |          | 位       |

| 无                | 失码          |            |      | 保证   |          |         |

| 模拟输入电压的          |             |            |      |      |          |         |

| <u>+1</u>        | 0 V         |            |      | 11.5 |          | kΩ      |

| ±:               | 5 V         |            |      | 6.7  |          | kΩ      |

| ±3.              | 33 V        |            |      | 5.4  |          | kΩ      |

| 0 V t            | o 10 V      |            |      | 6.7  |          | kΩ      |

| 0 V              | to 5 V      |            |      | 5.0  |          | kΩ      |

| 0 V              | to 4 V      |            |      | 5.4  |          | kΩ      |

| 数据吞吐速度           |             |            | l    |      | l        | l .     |

|                  | 英周期         | 采样加转换      | 4    |      |          | μs      |

| 吞                | <b>土率</b>   |            |      |      | 250      | kHz     |

| 直流特性             |             |            | •    | 1    | <u> </u> | T.      |

| 微分非约             | 栈性(DNL)     |            | -1   |      | 1        | LSB     |

| 积分非约             | 线性(INL)     |            | -7   |      | 7        | LSB     |

| 转换               | <b>·</b> 噪声 |            |      | 1    |          | LSB     |

| <b>井目和1171 子</b> | ±10V 范围     | 内部参考       | -0.5 |      | 0.5      | 0/ FGD  |

| 满量程误差            | 其他范围        | 0.1%外部固定电阻 | -0.5 |      | 0.5      | %FSR    |

| 满量程              | 误差漂移        | 内部参考       |      | ±7   |          | ppm/ °C |

| V# E 40 V0 V4    | ±10V 范围     | 外部参考       | -0.5 |      | 0.5      | FGF     |

| 满量程误差            | 其他范围        | 0.1%外部固定电阻 | -0.5 |      | 0.5      | %FSR    |

| 满量程误差漂移          |             | 外部参考       |      | +2   |          | ppm/ °C |

| 双极性零点误差          |             |            | -5   |      | 5        | mV      |

| 双极性零             | 点误差漂移       |            |      | ±0.4 |          | ppm/ °C |

| 单极性零点误<br>差      | 0~10V 范围    |            | -5   |      | 5        | mV      |

| 参数                                        | 条件                                                        | 最小值  | 典型值       | 最大值  | 单位      |

|-------------------------------------------|-----------------------------------------------------------|------|-----------|------|---------|

| 0~4V 和 0~5V<br>范围                         |                                                           | -3   |           | 3    |         |

| 单极性零点误差漂移                                 |                                                           |      | <u>+2</u> |      | ppm/ °C |

| 断电后恢复到额定精度                                | CAP引脚接1μF 电容                                              |      | 1         |      | ms      |

| 电源敏感性(V <sub>ANA</sub> = V <sub>D</sub> ) | $+4.75 \text{ V} < \text{V}_{\text{D}} < +5.25 \text{ V}$ | -8   |           | 8    | LSB     |

| 数字电源 V <sub>DIG</sub>                     |                                                           | 3.3  | 5         | 5.5  | V       |

| 交流特性                                      |                                                           |      |           |      | •       |

| 信噪失真比(SNDR)                               | f <sub>IN</sub> =1kHz                                     |      | 80.5      |      | dBFS    |

| 无杂散动态范围(SFDR)                             | f <sub>IN</sub> =1kHz                                     |      | 87.0      |      | dBFS    |

| 信噪比(SNR)                                  | f <sub>IN</sub> =1kHz                                     |      | 85.1      |      | dBFS    |

| 总谐波失真(THD)                                | f <sub>IN</sub> =1kHz                                     |      | -85.3     |      | dBFS    |

| 参考电压                                      |                                                           |      |           |      |         |

| 内部参考电压                                    |                                                           | 2.48 | 2.5       | 2.52 | V       |

| 内部参考电压驱动电流 (必须使用<br>外部缓冲)                 |                                                           |      | 1         |      | μΑ      |

| 内部参考漂移                                    |                                                           |      | 8         |      | ppm/ °C |

| 外部参考电压范围                                  |                                                           | 2.3  | 2.5       | 2.7  | V       |

| 外部参考负载电流                                  | 外部 2.5V参考电压                                               |      |           | 100  | μΑ      |

# 数字规格

除非另有说明,在  $T_A$ =-40  $\Upsilon$  至 85  $\Upsilon$ ,  $f_S$ =250 kHz,  $V_{ANA}$ =5V,  $V_{DIG}$ =3.3V~5.5V,使用内部参考电压和 0.1%,0.25W 固定电阻。

表 2 数字规格参数

|                   | 参数      | 条件                                           | 最小值                     | 典型值                 | 最大值                   | 单位  |

|-------------------|---------|----------------------------------------------|-------------------------|---------------------|-----------------------|-----|

| 数字                | 输入      |                                              |                         |                     |                       |     |

| $V_{IL}$          | 逻辑电平低   |                                              | -0.3                    |                     | 0.8                   | V   |

| $V_{\mathrm{IH}}$ | 逻辑电平高   |                                              | 2.0                     |                     | V <sub>DIG</sub> +0.3 | V   |

| $I_{IL}$          | 低电平输入电流 | V <sub>IL</sub> =0V                          |                         |                     | ±10                   | mA  |

| I <sub>IH</sub>   | 低电平输入电流 | V <sub>IH</sub> =5V                          |                         |                     | ±10                   | mA  |

| 数字                | 输出      |                                              |                         |                     | •                     |     |

|                   | 数据格式    |                                              |                         | 串行 16 位             |                       |     |

|                   | 数据编码    |                                              |                         | 二进制补码或直二进制          |                       |     |

|                   | 流水线延迟   |                                              |                         | 转换结果只有在完成转换<br>后才可用 |                       |     |

|                   | 数据时钟    |                                              |                         | 可选择的内部或外部数据<br>时钟   |                       |     |

|                   | 内部时钟    | EXT/INT Low                                  |                         | 9                   |                       | MHz |

|                   | 外部时钟    | EXT/INT High                                 | 0.1                     |                     | 26                    | MHz |

| $V_{OL}$          | 逻辑电平低   | $I_{SINK} = 1.6 \text{ mA}$                  |                         |                     | 0.4                   | V   |

| $V_{OH}$          | 逻辑电平高   | $I_{SOURCE} = 500 \text{ mA}$                | $V_{\mathrm{DIG}}$ -0.5 |                     |                       | V   |

|                   | 漏电流     | 高阻态,V <sub>OUT</sub> =0V to V <sub>DIG</sub> |                         |                     | ±5                    | μΑ  |

|                   | 输出电容    | 高阻态                                          |                         |                     | 15                    | pF  |

### 极限参数

| $V_{ANA}$ 至 AGND1/20.3V 至 6V                                                 |

|------------------------------------------------------------------------------|

| $V_{DIG}$ 至 DGND0.3V 至 6V                                                    |

| 模拟输入(R1 <sub>IN</sub> , R2 <sub>IN</sub> , R3 <sub>IN</sub> )电压至 AGND1/2±25V |

| 模拟参考输入 REF, CAP 电压至 AGND2+V <sub>ANA</sub> +0.3V to AGND2-0.3 V              |

| 数字输入电压至 DGND0.3V 至+V <sub>DIG</sub> +0.3V                                    |

| 最大结温 T <sub>J,MAX</sub>                                                      |

| 工作温度范围40℃至85℃                                                                |

| 存储温度范围65℃至150℃                                                               |

| ESD                                                                          |

| HBM4000V                                                                     |

| CDM500V                                                                      |

| Latch up 电流200mA                                                             |

对以上所列的最大极限值,如果器件工作在超过此极限值的环境中,很可能会对器件造成永久性破坏。在实际运用中,最好不要使器件工作在此极限值或超过此极限值的环境中。

本产品属于静电敏感器件。拿取时要采取合适的 ESD 保护措施,以免造成性能下降或功能失效。

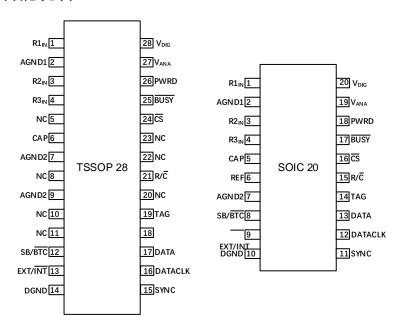

# 管脚(焊盘)配置及功能说明

图 2 SC1462 管脚(焊盘)配置(俯视图)

表 3 管脚定义

| 引脚名称                     | 引脚                        | 编号      | 」引脚类型 | 引脚功能                  |

|--------------------------|---------------------------|---------|-------|-----------------------|

| 71 MAY 127 17V           | TSSOP-28                  | SOIC-20 |       | J1,047-23,116         |

| AGND1                    | 2                         | 2       | G     | 模拟地                   |

| AGND2                    | 9                         | 7       | G     | 模拟地                   |

| $\overline{	ext{BUSY}}$  | 25                        | 17      | DO    | 输出繁忙位                 |

| CAP                      | 6                         | 5       | AO    | 参考电压缓冲电容              |

| $\overline{\mathtt{CS}}$ | 24                        | 16      | DI    | 芯片的选择信号               |

| DATA                     | 17                        | 13      | DO    | 串行数据输出                |

| DATACLK                  | 16                        | 12      | DIO   | 数据时钟                  |

| DGND                     | 14                        | 10      | G     | 数字地                   |

| EXT/INT                  | 13                        | 9       | DI    | 选择数据的外部时钟或内部时钟。       |

| NC                       | 5,8,10,11,18,20<br>,22,23 | /       |       | 无连接                   |

| PWRD                     | 26                        | 18      | DI    | 关断引脚                  |

| $R/\overline{C}$         | 21                        | 15      | DI    | 读/转换引脚                |

| REF                      | 7                         | 6       | AIO   | 输入/输出参考电压             |

| R1 <sub>IN</sub>         | 1                         | 1       | AI    | 模拟输入                  |

| R2 <sub>IN</sub>         | 3                         | 3       | AI    | 模拟输入                  |

| R3 <sub>IN</sub>         | 4                         | 4       | AI    | 模拟输入                  |

| $SB/\overline{BTC}$      | 12                        | 8       | DI    | 选择数据输出格式为直接二进制还是二进制补码 |

| SYNC                     | 15                        | 11      | DO    | 输出同步信号                |

| TAG                      | 19                        | 14      | DI    | 用于外部时钟模式的输入标志         |

| V <sub>ANA</sub>         | 27                        | 19      | P     | 模拟电源电压                |

| $V_{DIG}$                | 28                        | 20      | P     | 数字电源电压                |

上海芯炽科技集团有限公司所有, 未经允许, 不得外传

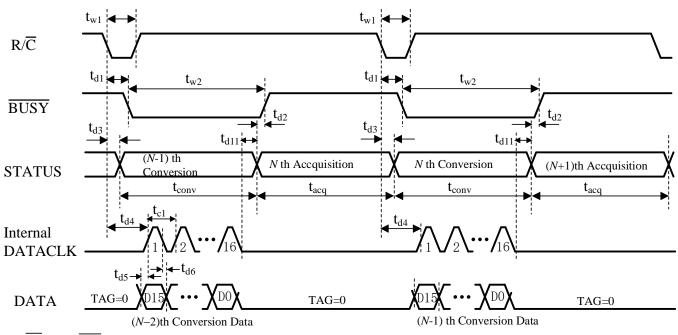

# 时序要求

表 4 时序要求

|                                     | 参数                                    | 最小值 | 典型值 | 最大值 | 单位 |

|-------------------------------------|---------------------------------------|-----|-----|-----|----|

| $t_{w1}$                            | 转换的脉冲时间                               | 40  |     |     | ns |

| $t_{d1}$                            | 从 R/C低电平到BUSY的延迟时间                    |     | 6   | 20  | ns |

| $t_{w2}$                            | BUSY低的脉冲时间                            |     |     | 2.2 | μs |

| $t_{d2}$                            | 转换之后BUSY的延迟时间                         |     | 5   |     | ns |

| t <sub>d3</sub>                     | 孔径延迟时间                                |     | 5   |     | ns |

| t <sub>conv</sub>                   | 转换时间                                  |     |     | 2.2 | μs |

| $t_{acq}$                           | 数据采集时间                                | 1.8 |     |     | μs |

| t <sub>conv</sub> +t <sub>acq</sub> | 周期时间                                  |     |     | 4   | μs |

| $t_{d4}$                            | R/C低到内部时钟 DATACLK 输出的延迟时间             |     | 270 |     | ns |

| t <sub>c1</sub>                     | 内部时钟 DATACLK 的周期时间                    |     | 110 |     | ns |

| t <sub>d5</sub>                     | 数据有效到内部时钟 DATACLK 变高的延迟时间             | 15  | 35  |     | ns |

| $t_{d6}$                            | 内部时钟 DATACLK 变低到数据有效的延迟时间             | 20  | 35  |     | ns |

| $t_{c2}$                            | 外部时钟 DATACLK 的周期时间                    | 35  |     |     | ns |

| $t_{w3}$                            | 外部时钟 DATACLK 的高电平持续时间                 | 15  |     |     | ns |

| $t_{w4}$                            | 外部时钟 DATACLK 的低电平持续时间                 | 15  |     |     | ns |

| t <sub>su1</sub>                    | R/C变高/低到外部时钟 DATACLK 变高的建立时间          | 15  |     |     | ns |

| $t_{su2}$                           | R/C变换到CS变换的建立时间                       | 10  |     |     | ns |

| t <sub>d7</sub>                     | DATACLK 变高到 SYNC 的延迟时间                | 3   |     | 35  | ns |

| $t_{d8}$                            | 数据有效的延迟时间                             | 2   |     | 20  | ns |

| $t_{d9}$                            | CS到上升沿的延迟时间                           | 10  |     |     | ns |

| t <sub>d10</sub>                    | CS和 R/C变低之后到上一个数据可得的延迟时间              | 2   |     |     | μs |

| $t_{su3}$                           | BUSY变换到第一个外部 DATACLK 的建立时间(读上一次转换的数据) | 5   |     |     | ns |

| $t_{su4}$                           | BUSY变换到第一个外部 DATACLK 的建立时间(读本次转换的数据)  | 1.2 |     |     | μs |

| t <sub>d11</sub>                    | 第一个外部时钟 DATACLK 到BUSY下降沿的延迟时间         |     |     | 1   | μs |

| t <sub>su3</sub>                    | TAG有效的建立时间                            | 0   |     |     | ns |

| t <sub>h1</sub>                     | TAG有效的保持时间                            | 2   |     |     | ns |

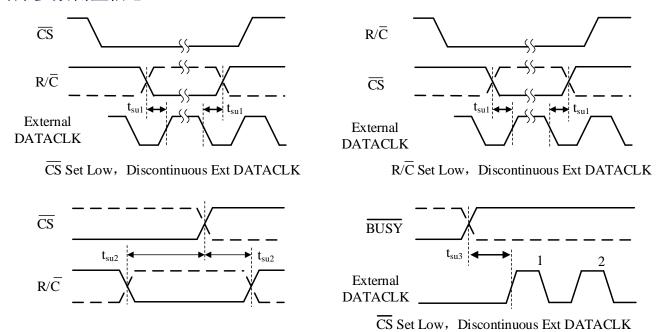

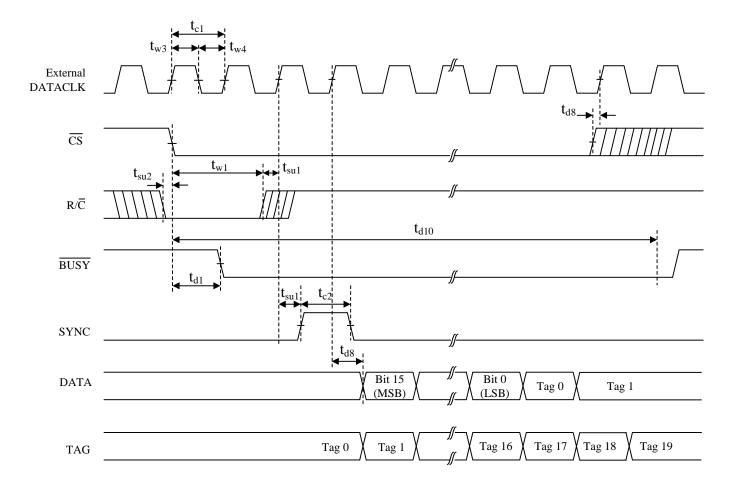

# 时序参数测量信息

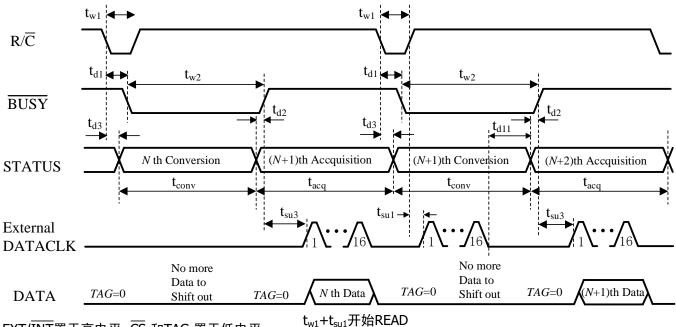

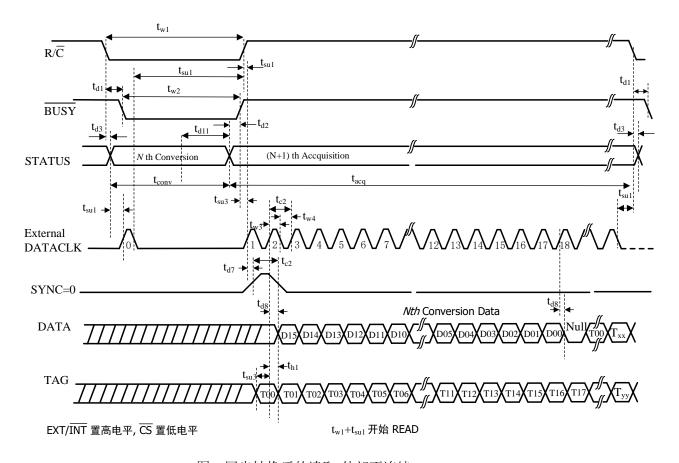

图 3 关键时序

CS, EXT/INT, TAG 置于低电平

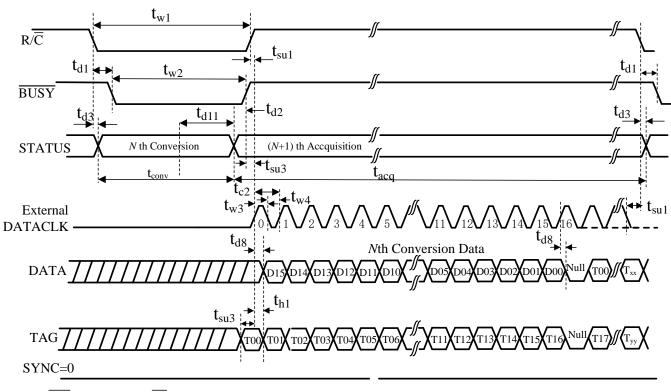

图 4 基本转换时序(内部 DATACLK-转换期间读取先前数据)

EXT/INT置于高电平, CS 和TAG 置于低电平

注意,当*N*=1时,不要在第一次转换期间,发送External DATACLK

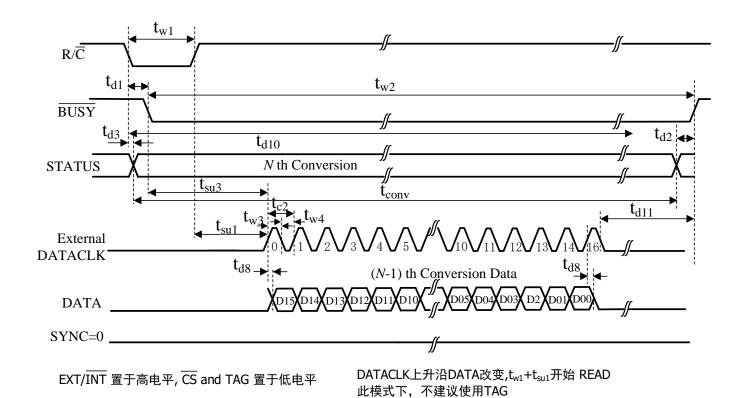

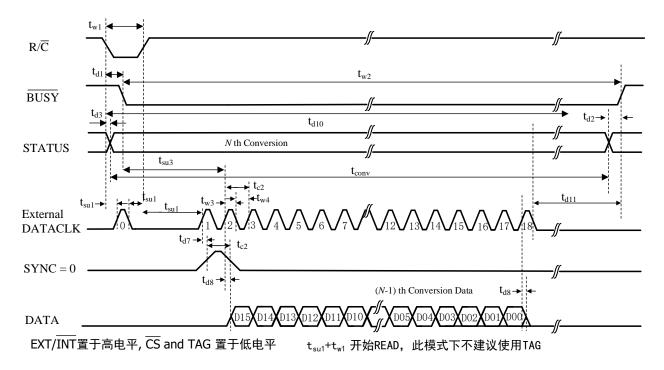

图 5 基本转换时序(外部 DATACLK)

EXT/INT 置于高电平, CS 置于低电平

tw1+tsu1 开始READ

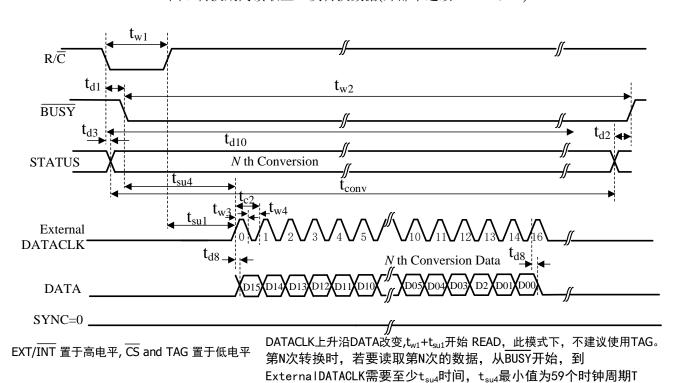

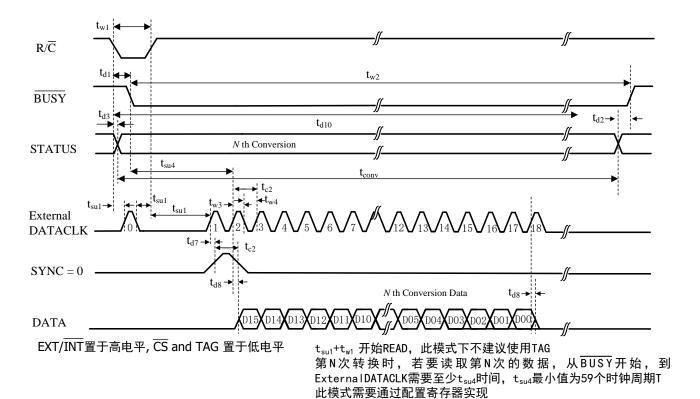

图 6 转换后读取(外部不连续 DATACLK)

图 7 转换期间读取上一次转换数据(外部不连续 DATACLK)

图 8 转换期间读取本次转换数据(外部不连续 DATACLK)

此模式需要通过配置寄存器实现

上海芯炽科技集团有限公司所有, 未经允许, 不得外传

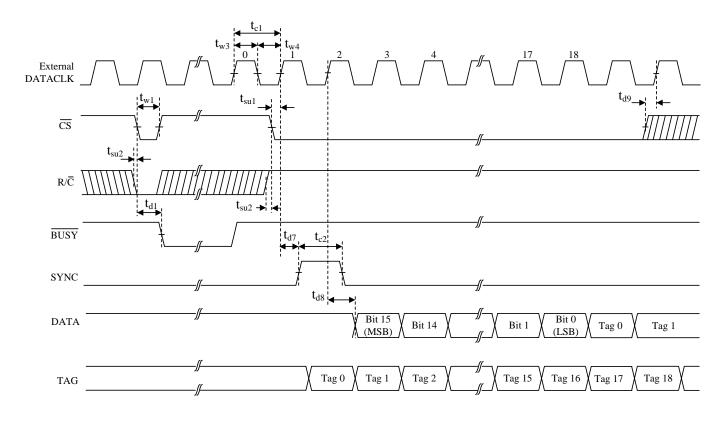

图 9 同步转换后的读取(外部不连续 DATACLK)

图 10 同步转换期间读取上一次转换数据(外部不连续 DATACLK)

图 11 同步转换期间读取本次转换数据(外部不连续 DATACLK)

图 12 转换后连续外部时钟 DATACLK(EXT/INT置高电平)读取的转换和读取时序(不推荐)

图 13 转换期间使用连续外部时钟 DATACLK(EXT/INT并置高电平)读取先前的转换结果的转换和读取时序(不推荐)

### 使用说明

### 基本操作

SC1462 中有两个转换控制信号: CS和 R/C,这两个信号在内部一起作用。启用转换功能时必须将CS置为低电平;必须让转换信号有效,将 R/C置为低电平。这两个信号先调低哪一个都是可行的,转换会从第二个信号的下降沿开始。转换开始时BUSY变为低电平,并在该转换的数据移位到内部存储寄存器后返回高电平。当BUSY变为高电平的时候,采样过程开始。

为了减少控制使用引脚的数量,可以将CS一直置于低电位,此时,R/C引脚专门控制转换和数据读取。在外部时钟模式下,只要 R/C为高电平且外部时钟有效,SC1462就会输出数据。在内部时钟模式下,无论CS和 R/C的状态如何,每个转换周期都会输出数据。SC1462提供一个 TAG输入,用于将多个转换器级联在一起。

### 读取数据

BUSY恢复为高电平时,转换结果可用。SC1462可以用直接二进制或二进制补码格式输出串行数据,由 SB/BTC引脚控制。MSB表示数据最高位,最先输出。上电后立即进行的第一次转换的结果是无效的。

EXT/INT引脚可以控制数据输出的时钟类型,内部时钟或外部时钟均可用;如果使用外部时钟,则可使用 TAG输入,以菊花链的形式将多个 SC1462 数据引脚链接在一起。

#### 内部 DATACLK

在内部时钟模式下,前一次转换的数据会在当前的转换周期内输出。由于内部数据时钟与内部转换时钟同步,因此不会干扰转换过程。

当 EXT/INT为低电平时,DATACLK 引脚变为输出。在满足时序 t<sub>8</sub>之后,会在每次转换开始时产生 16个时钟脉冲,在转换期间只能读取前一次的转换结果。当 DATACLK 处于非活动状态时,会返回到低电平。与该时钟同步的 16 位串行数据从数据引脚移出,每个位在上升沿和下降沿可用。DATA 引脚返回到传输开始时所检测到的 TAG 引脚的输入状态。

### 外部 DATACLK

外部时钟模式提供多种方法来检索转换结果。但是,由于外部时钟无法与内部转换时钟同步,因此必须小心,避免损坏数据。

当 EXT/INT设置为高电平时,R/C和CS信号控制读状态。当启用读取状态时,前一个转换结果被移出 DATA 引脚,该操作与连接到 DATACLK 引脚的外部时钟同步。每一位数据都可以在下降沿和上升沿使用。最大的外部时钟速度为 28.5MHz,允许数据在转换开始或采样开始时快速移出。

当使用外部时钟时,有几种可用的操作模式。建议外部时钟只在读数据时运行。这是不连续时钟模式。由于外部时钟没有与控制转换的内部时钟同步,外部时钟的微小变化可能会导致冲突,破坏转换过程,无法保证外部时钟持续运行。特别重要的是,外部时钟在转换周期的后半部分不会运行(约为 tan 指定的时间段,请参阅时序要求表)。

在不连续时钟模式下,数据可以在转换期间或采样期间读取,有无 SYNC 信号均可。转换期间读取的数据必须满足 tall 时序要求。在开始转换之前,必须完成采样期间的数据读取。

无论在采样期间读还是在转换期间读,只要外部时钟有至少一个上升沿,即使在非读状态,也会生成 SYNC 脉冲。在具有 SYNC 模式的不连续外部时钟模式中,在读取命令后的第一个时钟的上升沿后会产生一个 SYNC 脉冲,数据在 SYNC 脉冲后被移出。SYNC 脉冲可以在下一个下降沿和下一个上升沿上检测到。以此类推,每个位可以先在下降沿上读,然后在下一个上升沿上读。因此,在读命令后,需要 17 个时钟脉冲的下降沿来读取数据。对于上升沿的读数至少需要18 个时钟脉冲。

如果时钟在非读状态时完全不活动,则不会产生同步 SYNC 脉冲。在这种情况下,SC1462 会在第一个时钟的上升沿输出数据最高位 MSB。MSB 可以在第一个时钟下降沿或下一个时钟上升沿上读取。在这种没有 SYNC 的不连续外部时钟模式中,需要 16 个时钟读取下降沿上的数据,17 个时钟读取上升沿上的数据。

上述不连续外部时钟读取所需要的脉冲个数,与 SYNC 和读取时钟沿的关系,如表 5 所示。

描述

需要的数据传输脉冲个数

带有 SYNC

不带 SYNC

在DATACLK的下降沿读取

17

16

在DATACLK的上升沿读取

18

17

表 5 DATACLK 脉冲信息

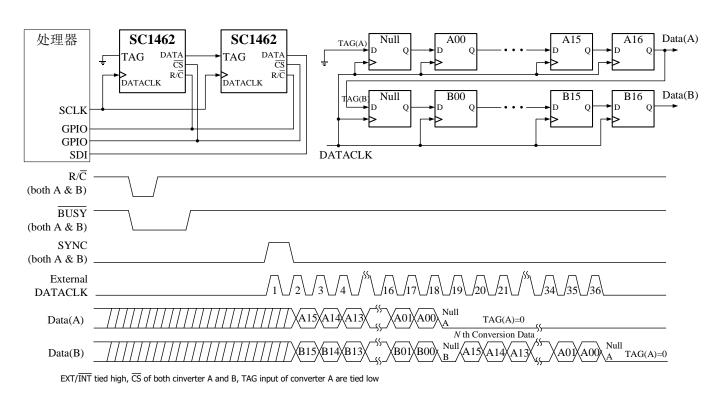

### TAG 特性

TAG特性允许从多个 SC1462 转换器读取单个串行线上的数据。转换器级联在一起,使用 DATA 引脚作为输出,使用 TAG 引脚作为输入,如图 14 所示。最后一个转换器的 DATA 引脚驱动处理器的串行数据输入。然后,数据通过每个转换器转移到串行数据线上,与外部提供的数据时钟同步。内部时钟不能用于此配置。

在采样期间,推荐使用不连续的外部数据时钟。由于在转换期间没有足够的时间从多个转换器读取数据而不违反 t<sub>dl1</sub> 约束(请参阅外部 DATACLK 部分),因此必须在采样期间读取数据。采样周期必须足够长,以允许在开始新的转换之前读取所有数据字。

在图 14 中,NULL 位将数据字与每个转换器隔开。DATA 引脚在 READ 循环结束时的状态反映了 TAG 引脚在循环开始时的状态。这在所有 READ 模式中都是正确的,包括内部时钟模式。例如,当单个转换器在内部时钟模式下使用时,TAG 引脚的状态决定了所有 16 位移出后 DATA 引脚的状态;当多个转换器级联在一起时,这种状态形成分隔单词的 NULL 位。因此,第一个转换器的 TAG 引脚接地如图 14 所示,NULL 位在每个数据字之间变为零。

图 14 单次转换 TAG 特性的时序(使用外部 DATACLK)

### 模拟输入

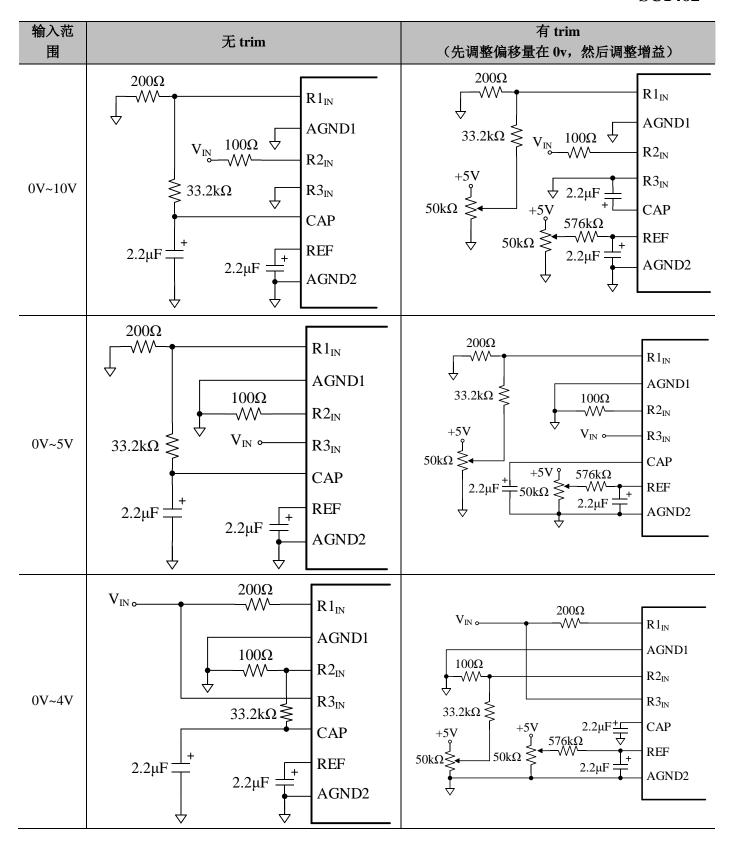

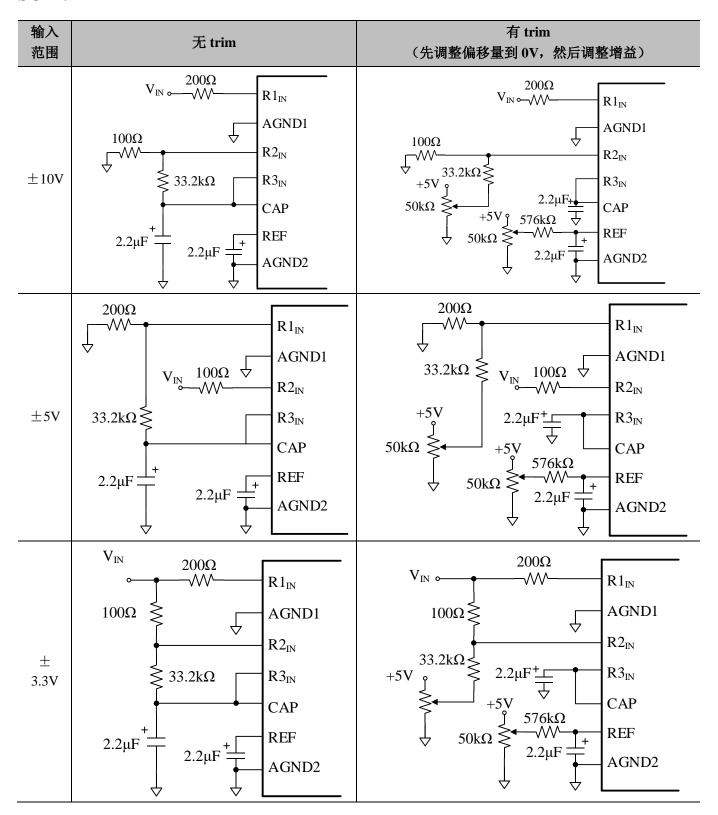

SC1462 有 6 个模拟输入范围,如表 6 所示。偏移和增益规格采用 0.1%, 0.25W,外部电阻进行出厂校准,如图 16 和图 17 所示。如果可以接受较大的增益和偏移误差,或者使用软件校准,则可以省略掉外部电阻。如图 16 和图 17 所示的硬件微调电路可以将误差降至零。

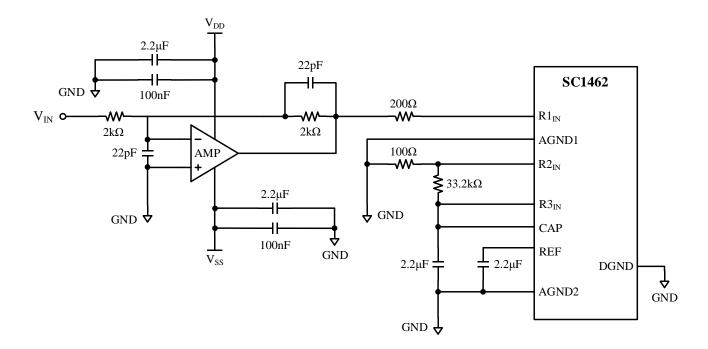

模拟输入引脚 R1<sub>IN</sub>、R2<sub>IN</sub>、R3<sub>IN</sub>具有±25V 过压保护功能。输入信号必须参考 AGND1。这最大限度地减少了模拟设计中典型的接地回路问题。模拟输入应该由低阻抗源驱动,典型驱动电路如图 15 所示。

SC1462 可以使用内部 2.5V 参考电压或外部参考电压工作。连接到引脚 REF 的外部参考电压绕过了内部参考电压。外部参考必须驱动将引脚 REF 与内部参考分开的 4kΩ 电阻。负载随内部和外部参考电压之间的差异而变化。外部参考电压范围为 2.3V~2.7V,内部参考电压约为 2.5V。无论是内部的还是外部参考电压,都会用一个内部缓冲器在引脚 CAP 进行缓冲。

SC1462 使用  $2.2\mu$ F 电容连接到引脚 CAP 和 REF 进行工厂测试。每个电容器应放置尽可能接近其引脚。引脚 REF 上的电容限制了内部参考噪声,若此电容较小,可能会降低信噪比 SNR 和信噪失真比 SINAD。引脚 CAP 上的电容稳定内部参考缓冲器的电压,并在转换过程中为 CDAC 提供充电的电荷,小于  $1\mu$ F 的电容可能会导致缓冲变得不稳定,无法为 CDAC 提供足够的电荷。该部件的测试规格为  $2.2\mu$ F。这些补偿电容器的等效串联电阻(ESR)也是至关重要的,总 ESR 必须小于  $3\Omega$ 。

内部参考电压和缓冲器不能驱动外部负载,否则会降低性能。内部参考电压上的任何负载都会导致  $4k\Omega$  电阻上的电压下降,并影响增益。内部缓冲器能够驱动 $\pm 2mA$  的负载,但任何负载都可能导致 CDAC 参考的扰动,降低性能。需要指出的是,SC1462 不需要第二个高速放大器作为缓冲来隔离 CAP 引脚与  $R3_{IN}$  引脚中依赖于信号的电流。

外部参考电压范围为 2.3V~2.7V。参考电压决定了最小有效位(LSB)的大小。参考电压越大, LSB 越大, 信噪比越高。较小的参考电压会降低信噪比。

图 15.典型驱动电路((±10v, 无 trim)

表 6 输入范围连接(参见图 29 和图 30 的完整信息)

| 模拟输入范围 | R1 <sub>IN</sub> 连 200Ω 电阻到 | R2 <sub>IN</sub> 连 100Ω 电阻到 | R3连接         | 阻抗     |

|--------|-----------------------------|-----------------------------|--------------|--------|

| ±10V   | V <sub>IN</sub>             | AGND                        | CAP          | 11.5kΩ |

| ±5V    | AGND                        | V <sub>IN</sub>             | CAP          | 6.7kΩ  |

| ±3.33V | V <sub>IN</sub>             | V <sub>IN</sub>             | CAP          | 5.4kΩ  |

| 0~10V  | AGND                        | $V_{\rm IN}$                | AGND         | 6.7kΩ  |

| 0~5V   | AGND                        | AGND                        | $V_{\rm IN}$ | 5.0kΩ  |

| 0~4V   | V <sub>IN</sub>             | AGND                        | $V_{\rm IN}$ | 5.4kΩ  |

表 7 控制真值表

| 特定功能                    | CS   | R/C  | BUSY | EXT/INT | DATACLK | PWRD | SB/BTC | 操作                                 |

|-------------------------|------|------|------|---------|---------|------|--------|------------------------------------|

| 使用内部时                   | 1=>0 | 0    | 1    | 0       | output  | 0    | X      | 从转换 n-1 在 Data 上打卡                 |

| 钟启动转换 和输出数据             | 0    | 1=>0 | 1    | 0       | output  | 0    | Х      | 的数据同步到 DATACLK<br>上输出的 16 个时钟脉冲    |

|                         | 1=>0 | 0    | 1    | 1       | input   | 0    | X      | 启动转换 n                             |

|                         | 0    | 1=>0 | 1    | 1       | input   | 0    | X      | 启动转换 n                             |

| 使用外部时<br>钟启动转换<br>和输出数据 | 1=>0 | 1    | 1    | 1       | input   | X    | х      | 输出带或不带 SYNC 脉冲<br>的数据。详见读取数据小<br>节 |

| 作机口致功                   | 1=>0 | 1    | 0    | 1       | input   | 0    | X      | 输出带或不带 SYNC 脉冲                     |

|                         | 0    | 0=>1 | 0    | 1       | input   | 0    | х      | 的数据。详见读取数据小<br>节                   |

| 无动作                     | 0    | 0    | 0=>1 | X       | X       | 0    | X      | 这是可接受的情况                           |

|                         | X    | X    | X    | X       | X       | 0    | х      | 模拟电路供电,转换可以<br>进行                  |

| 关断信号                    | X    | X    | Х    | X       | X       | 1    | х      | 模拟电路被禁用,以前转<br>换的数据保存在输出寄存<br>器中   |

| 选择输出格                   | X    | X    | X    | X       | X       | X    | 0      | 串行数据以二进制 2 的补<br>码格式输出             |

| 式                       | X    | х    | Х    | X       | X       | X    | 1      | 串行数据以直接二进制格<br>式输出                 |

表 8 输入码和理想输入电压

|                                     |               |               |               |               |               |               |                              | 数字               | 输出                           |      |

|-------------------------------------|---------------|---------------|---------------|---------------|---------------|---------------|------------------------------|------------------|------------------------------|------|

| 描述                                  | 模拟输入          |               |               |               |               |               |                              | 削补码<br>BTC<br>W) | 二流<br>(SB/<br>HIC            | BTC  |

|                                     |               |               |               |               |               |               |                              | HEX              | BINA<br>RY                   | HEX  |

| Full-<br>scale<br>range             | ±10V          | ±5V           | ±3.33V        | 0V~10V        | 0V~5V         | 0V~4V         |                              |                  |                              |      |

| LSB                                 | 305μV         | 153μV         | 102μV         | 153μV         | 76μV          | 61µV          |                              |                  |                              |      |

| Full-scale (FS-1LSB)                | 9.999695<br>V | 4.999847<br>V | 3.333231<br>V | 9.999847<br>V | 4.999924<br>V | 3.999939<br>V | 0111<br>1111<br>1111<br>1111 | 7FFF             | 1111<br>1111<br>1111<br>1111 | FFFF |

| Midscal<br>e                        | 0V            | 0V            | 0V            | 5V            | 2.5V          | 2V            | 0000<br>0000<br>0000<br>0000 | 0000             | 1000<br>0000<br>0000<br>0000 | 8000 |

| One<br>LSB<br>below<br>midscal<br>e | -305μV        | 153μV         | ±102μV        | 4.999847<br>V | 2.499924<br>V | 1.999939<br>V | 1111<br>1111<br>1111<br>1111 | FFFF             | 0111<br>1111<br>1111<br>1111 | 7FFF |

| -Full<br>scale                      | -10V          | -5V           | 3.333333<br>V | 0V            | 0V            | 0V            | 1000<br>0000<br>0000<br>0000 | 8000             | 0000<br>0000<br>0000<br>0000 | 0000 |

图 16 单极输入范围的偏移/增益电路

图 17 双极输入范围的偏置/增益电路

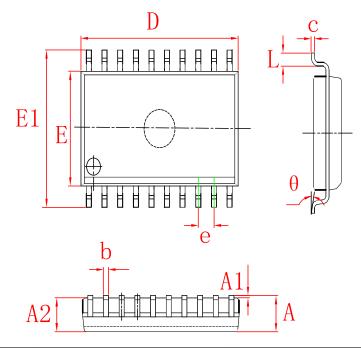

# 外形尺寸

| Symbol   | Dimensions In | n Millimeters | Dimensions | In Inches |

|----------|---------------|---------------|------------|-----------|

| Syllibol | Min           | Max           | Min        | Max       |

| Α        | 2. 350        | 2. 650        | 0. 093     | 0. 104    |

| A1       | 0. 100        | 0. 300        | 0. 004     | 0. 012    |

| A2       | 2. 100        | 2. 500        | 0. 083     | 0. 098    |

| b        | 0. 330        | 0. 510        | 0. 013     | 0. 020    |

| С        | 0. 204        | 0. 330        | 0.008      | 0. 013    |

| D        | 12. 520       | 13. 000       | 0. 493     | 0. 512    |

| E        | 7. 400        | 7. 600        | 0. 291     | 0. 299    |

| E1       | 10. 210       | 10. 610       | 0. 402     | 0. 418    |

| е        | 1. 27         | 70 (BSC)      | 0. 05      | 50 (BSC)  |

| L        | 0. 400        | 1. 270        | 0. 016     | 0. 050    |

| θ        | 0°            | 8°            | 0°         | 8°        |

图 18 20 脚 SOIC 封装尺寸图

# 订购信息

表 9 产品订购信息

| 型号     | 温度范围     | 物料编号         | 封装类型    | 包装形式 |

|--------|----------|--------------|---------|------|

| SC1462 | -40~85°C | SC1462GAOUMX | SOIC-20 | Tube |

注: 也可支持 TSSOP-28 封装